Комплетан 2Д Фласх чип омогућен системом интеграција

Фласх Цхип измишљоте

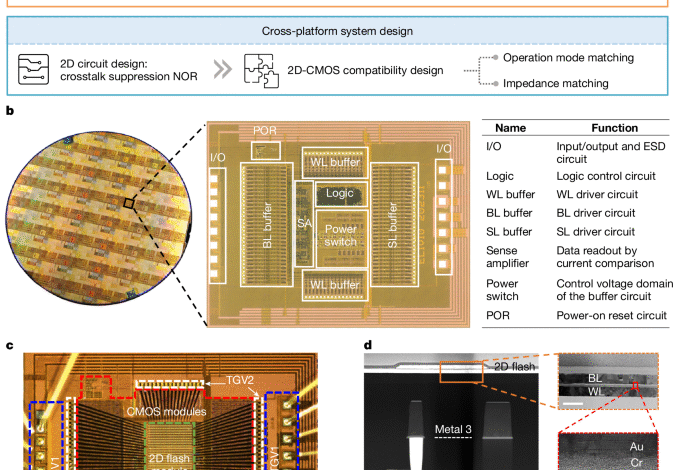

ЦМОС круг је измишљен у стандардном ЦМОС ливницу користећи поступак од 0,13 у μм. Примљени од 8-инчни резифер имао је дебљину слоја пасивације од око 800 нМ, са унапред резервисаним виасом на лучким јастучићима И / О (ТГВ1 региона) и ВЛ / БЛ / СЛ пуфера (регион ТГВ2). Вафар је пресечен на појединачно умре, свака са димензијом од 5 мм × 5 мм (укључене су четири скупа идентичних кругова). Третмани за одступање од полимерне посредовања обављени су на ЦМОС супстрат пре интегрисања 2Д блица. ЦМОС супстрат је очишћен натапањем у ацетону 12 х, а затим слиједећи премаз са фоторесистичким (С1818) и уклањањем фоторисисте Н-метил-2-пиролидон (НМП) натопите 12 х.

Литографија за директно напишавање коришћена је за излагање Виндовс-а у региону ТГВ2, а евапорација е-снопа (ЕБЕ) је коришћена за попуњавање виаса са 5/500 НМ ЦР / АУ. ВЛС је дефинисан коришћењем литографије директног писања, а затим депонирање од 5/100/5 НМ ЦР / АУ / ПТ. О2 Лечење у плазми (50 В, 20 с) коришћено је за додатно чишћење и активирање површине за диелектрично депоновање. 13-НМ ХФО2 Слој блокирања је депонован помоћу тармалног таложења атомског слоја. Тетракис (етилметиламино) хафниум реагује са водом на 150 ° Ц формира се ХФО2. Узорак плутајуће капије је дефинисан литографијом директног писања, а 3-НМ ПТ је депоновао ЕБЕ. О2 Опет у плазми поново је изведено. Накнадно, 7-НМ ХФО2 Слој тунела је депонован коришћењем истог система депоновања атомског слоја. ВИАС путем ХФО-а2/ ПТ / ХФО2 Стацк меморије је дефинисан директним писма литографија и јељених коришћењем реактивног ионског јеткања (АР + ЦХФ)3175 В, 255 с) и ЕБЕ је затим коришћен за положавање 5/50 НМ ЦР / АУ слоја да би испунио виас. Хемијска параловање паре монолаиер мос2 (Купљено од Сикцарбонске технологије) пребачен је на стацк меморије помоћу постепеног поступка преноса преноса. Минимална брзина приступа између мос2 А супстрат се пажљиво контролише да је низак од 500 нМ по корак помоћу опреме за пренос прилагођене прилагођене. Полистирен је коришћен као подршка слоја због свог великог младог модула да се избегне набора. Полистиренски носач је уклоњен натапање у толуену током 12 х. Моћ2 канали су узорковани директним писма литографија и јеткани од2 плазма (30 В, 20 с). Узорак је натопљен у НМП-у током 12 х да уклони фоторисисте. Да у моску у потпуности ослобађа стрес и ваздушне празнине2вишеструко жарење у ан2 Атмосфера (200 ° Ц, 3 х) извршена је за велике фолије и траке у узорку. Адхезија између мос2 А подлоге се такође може побољшати током ових процеса. БЛС и СЛС су дефинисани литографијом директној писању, праћено депоновањем од 5/100 НМ ЦР / АУ користећи ЕБЕ. За израду 2Д блица на сију2/ СИ подлоге, поступак који укључује виону горе наведено није потребно.

Да бисте пасивили 2Д Фласх модул, слој фоторесисте С1818 био је прекривен на узорку. ТГВ1 регион И / О модула био је изложен директивној литографији за повезивање жица. Чип је упакован коришћењем керамичког двоструког линијског пакета (ДИП 24).

Дизајн ланца претварача модула пуфера

Према логичкој теорији напора, укупни логички напор, одређен омјером оптерећења (10 пф у нашем случају, с обзиром на дизајнерску маржама) у инхерентно улазно капацитет ЦМОС претварача (2 ФФ, одлучује одабраном ЦМОС технологијом), требало би да се дистрибуира преко одабраног броја инвертерских фаза. Вријеме кашњења ширења претворни ланац у међуспремнику може се израчунати

$$ {т} _ {{\ рм {п}}} = {т} _ {{\ рм {п}} 0} \ матхеп {\ сум} \ лимит_ {ј = 1} ^ {н} \ лево (1+ \ фрац {г}} _ {\ 1}} {\ гамма {\ рм {г}}, ј}} \ тачно) $$

(1)

где Н је број фаза ланца претварача, Цг,ј је капацитет капије за јТХ ИНВЕРТЕР, Цг,Н+1 је дефинисано као оптерећење капацитета, овде паразитски капацитет 2Д меморије, тп0 је унутрашње кашњење претварача и Γ је параметар зависан од процеса, обично близу 1.

За оптимизовани дизајн, капацитет капије (и величина претварача) треба да буде геометријска средства суседних претварача, таквих да

$$ {ц} _ {{\ рм {г}}, ј} = \ скрт {ц} _ {{\ рм {ц} _ {{\ рм {г}}, ј + 1}}, {\ рм {где}} \; ј = 2, \ ЛДОТС, н $$

(2)

и оптимизовано време одлагања ширења може се написати као

$$ {т} _ {{\ рм {п}}} = н {т} _ {{\ рм {п}} 0} \ \ скрт (н) {\ фрац {\ рм {г}}, н + 1}} {{\ рм {г}}, 1}}} / \ гамма \ тачно) $$

(3)

Обично, ЦГ, 1 је минимална капацитијска капацитета претварача за одређени процес – у нашем раду, 2 ФФ-и Цг,Н+1 је 10 пф. Стога је оптимизовано Н За претворни ланац је 6 са кашњењем ширења од око 27.3тп0док Н= 4 је довољна са кашњењем од око 30.7тп0 и нуди користи везане за величину пуфера. За претварач сваке фазе, однос возача је \ (\ скрт (н) {\ фрац {ц} _ {{\ рм {г}}, н + 1}} {{\ рм {г}}, 1}}} \ цца 8 \)а оптимизирани ланац возача дизајниран је као што је приказано на Сл. 3Ц.

Карактеризација материјала

Узорци спремни за спремни из Тем-а припремљени су користећи Ин СИТУ ФИБ-оут технику листиће на ФЕИ СТРАТА Г4 ХКС ДУАЛ-БЕАМ ФИБ скенирању електронског микроскопа. Узорци су били затворени са пуцњавом електронско-снопом ПТ и ИОН-БЕАМ ПТ пре глодања. Слике стабљике и термама заробљене су са термоуцифичним тецнаи з аберационим преносом преносом електронског микроскопа на убрзавању напона од 200 кВ. Енерги-дисперзивна спектра добијена је у режиму стабљике помоћу Супер Кс Феи система. Слике уређаја АФМ уређаја је мерена МФП-3Д пореклом + (Асил Ресеарцх, Окфорд Инструментс) систем. Оптичке слике су заробљене оптичким микроскопом (Олимпус БКС53М) и продужени микроскоп (Кетеенце ВХКС-6000).

Електрична мерења

Електрична карактеризација самосталних 2Д флеш уређаја и низ 4 × 32 изведена је на собној температури и под атмосферским условима (осим теста за задржавање) у станици сонде (каскадни самит 11000 тип). Тест задржавања је спроведен у прилагођеној вакуумској станици сонде. Пулси напона су генерисани користећи анализатор параметара полуводича (Б1500, Кеисигхт). Таласни облик је заробљен помоћу осцилоскопа (ДПО 5204, Тектроник).

Електрична карактеризација 2Д Фласх чипа извршена је са наменским системом испитивања чипа. Агрегитарни генератор таласа (33120 А, Агилент) нуди сигнале сата, надгледати осцилоскоп (ДСОКС1204А, Кеисигхт). ДЦ напајање (Е36312А, Кеисигхт) нуди ДЦ сигнале потребне за тестирање чипа, укључујући -1 В, -5 В, 2 В, 3 В, 5 В и 9 В. Хост Цомпутер нуди софтверски интерфејс и учитава тест програм на ФПГА. ФПГА преноси наредбу са рачунара домаћина на И / О портове 2Д Фласх Цхип-а. Паковани 2Д Фласх чип смештен је у тестну утичницу компатибилан са ДИП пакетом пре тестирања.